To reuse the same lines of code again and again methods are used. System Verilog supports two types of methods.

(1) Function

(2) Task

Function:

- Delayed can NOT use in the function.

- Task WITHOUT delay can call in the function. It shouts only WARNING, not an ERROR.

- The function calls another function.

- The function can return value.

Task:

- Delayed can be inserted in the task.

- The task with DELAY can be called in the task.

- The function also can call in the task.

- The task can NOT return value.

The user can NOT call a task in function. Is it true? Is it shouts an ERROR?

NOT ALWAYS. The user can call a task in function if the definition of a task should NOT contain delay.

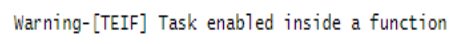

WITHOUT delay Warning: "warning-[teif] Task enabled inside a function"

WITH delay Error: "Function "function_name" has illegal use of delay or synchronization"

WITH delay Error: "Function "function_name" has illegal use of delay or synchronization"

USER WANT CODE:

To run simulation click on below link:

Link: https://www.edaplayground.com/x/2uZ8

(1) Function

(2) Task

Function:

- Delayed can NOT use in the function.

- Task WITHOUT delay can call in the function. It shouts only WARNING, not an ERROR.

- The function calls another function.

- The function can return value.

Task:

- Delayed can be inserted in the task.

- The task with DELAY can be called in the task.

- The function also can call in the task.

- The task can NOT return value.

The user can NOT call a task in function. Is it true? Is it shouts an ERROR?

NOT ALWAYS. The user can call a task in function if the definition of a task should NOT contain delay.

WITHOUT delay Warning: "warning-[teif] Task enabled inside a function"

USER WANT CODE:

function hello();

$display("This is Hello function");

Hi(); // CALL TASK(without delay) INSIDE FUNCTION

endfunction

task Hi();

//#1; // without delay

$display("This is Hi task");

hello();

endtask

module top();

initial

begin

hello(); // Call function

//Hi(); // call task

end

endmodule

To run simulation click on below link:

Link: https://www.edaplayground.com/x/2uZ8